Host Ergebnis

Energieeffiziente Analyse hochvolumiger Sequenzdaten mit rekonfigurierbaren Architekturen

# SeqAn@FPGA - Energieoptimierte Genomsequenzierungsbibliothek für energieeffiziente programmierbare Mikroelektronik in Rechenzentren

### Projektinformation

#### **Motivation:**

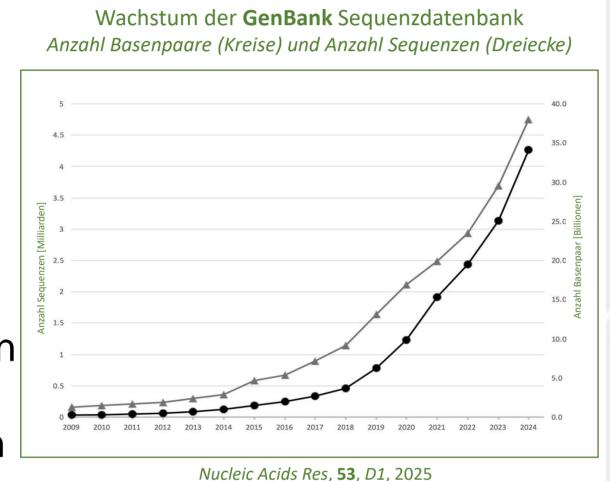

- exponentielles Datenwachstum durch Next-Gen Sequencing

- künftig wachsende Bedarfe mit personalisierter Medizin

- CO<sub>2</sub>-Einsparung im Hochdurchsatzrechnen

#### Ziel des Vorhabens

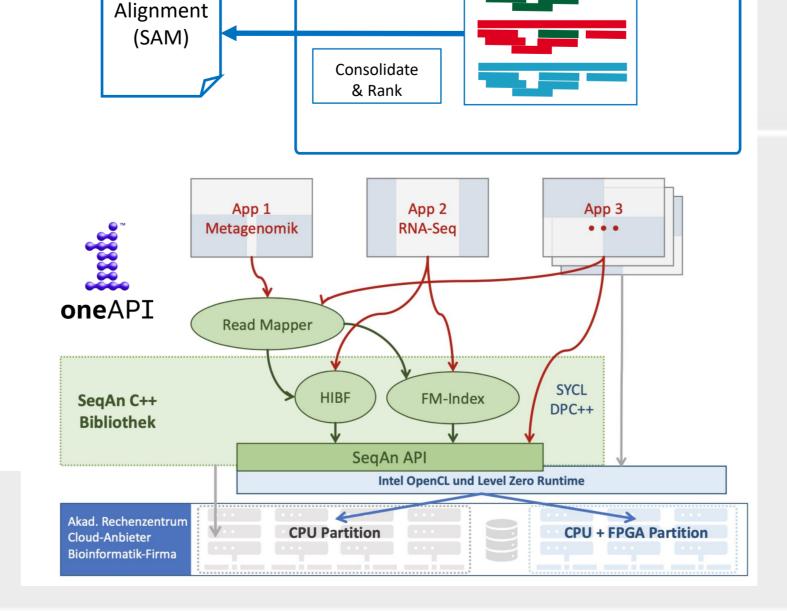

Implementierung von Schlüsselfunktionen der SegAn Software-Bibliothek für Analysen genomischer Sequenzen auf nutzerprogrammierbaren integrierten Schaltkreisen (Field Programmable Gate Array)

#### Technologie & Anwendungsfelder

- Zielplattformen: Rekonfigurierbare Architekturen mit Field-Programmable Gate Arrays (FPGA)

- Hochdurchsatzanalyse biologischer Sequenzdaten

- Workflows für personalisierte Medizin

- SeqAn für Patientenversorgung & Forschung

## **Ergebnisse und Erkenntnisse**

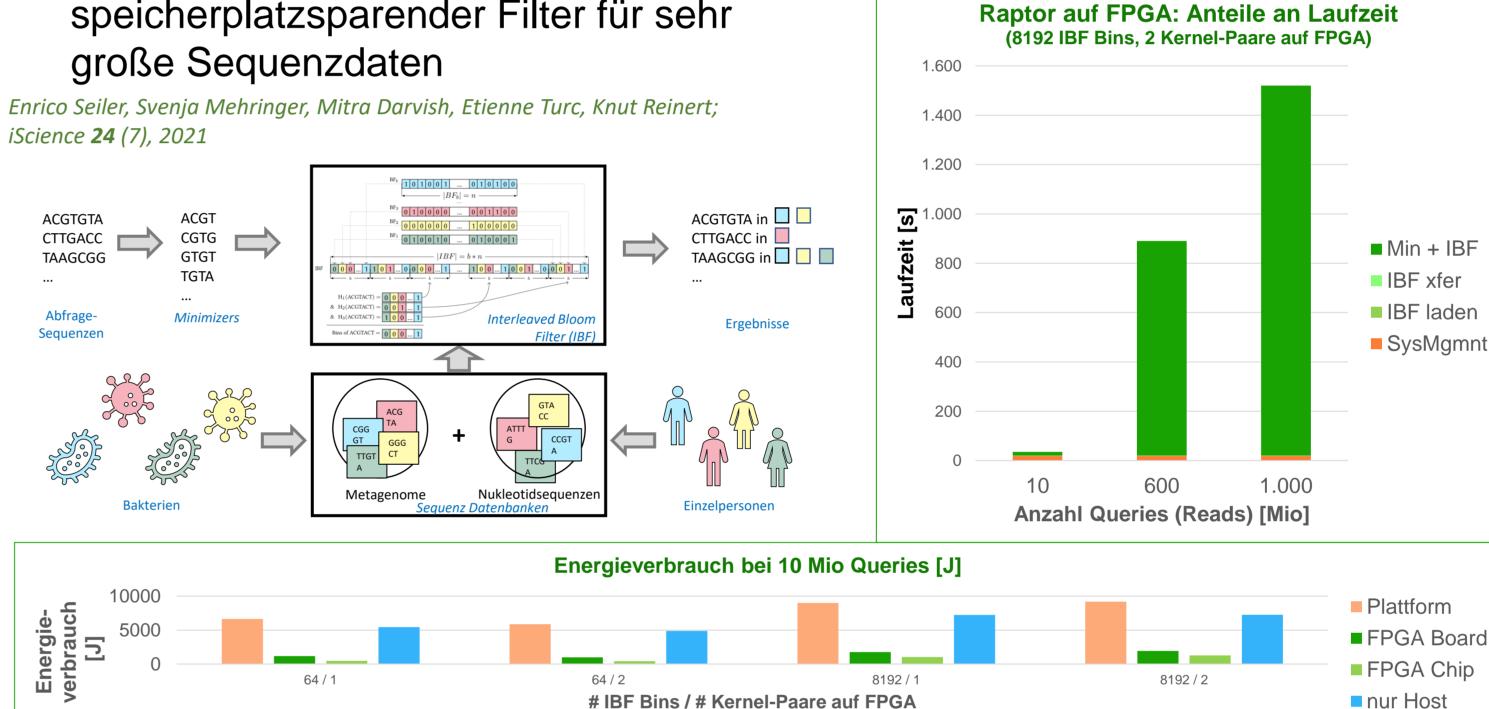

#### Raptor mit IBF auf FPGA

Raptor: ein schneller und speicherplatzsparender Filter für sehr große Sequenzdaten

Host Queries

# IBF Bins / # Kernel-Paare auf FPGA **IBF** Energiereduktion Energiereduktion **Kernel auf Device: Server Plattform:** Bins FPGA- vs. nur-CPU-Plattform FPGA vs. CPU 64 7,7 x6,2 x5,3 x8192 2,4 x

FPGA: Intel Agilex 7 auf BittWare IA-840 CPU: 2x AMD EPYC 9654 (Genoa) auf Lenovo ThinkSystem SD665 V3

Mapping

#### Innovation & Ausblick

- hohes Energieeinsparpotenzial mit FPGA

- SYCL-Implementierung in SeqAn erlaubt transparenten Zugriff auf FPGAs

- SegAn ermöglicht sehr hohe Breitenwirksamkeit

- Herausforderung HLS-Ökosystem

- alternative Datenfluss-Architekturen

Energieverbrauch

vom Host typisch

→ Host-less

Infrastrukturen

80%!

# Kontakt

- Prof. Dr. Knut Reinert Freie Universität Berlin Knut.Reinert@fu-berlin.de

- **Dr. Thomas Steinke** Zuse-Institut Berlin steinke@zib.de

## Projektziele und Methodik

- signifikante Energiereduktion für Analysen von Genomsequenzen

- Demonstrator: Read Mapper mit DREAM-Index

- Implementierung der Datenstrukturen Hierarchical Interleaved Bloom Filter (HIBF) und FM-Index aus SegAn auf FPGA

- Nutzung der Vorteile von FPGAs:

- Algorithmus definiert Hardware-Design

- optimale Repräsentation von Sequenzdaten (z.B. DNA mit 4 Bit je Element)

- o effiziente Bit-/String-Operationen

- Nutzung des High-Level Synthesis (HLS) Ansatzes für Produktivität ("Programmierung" eines FPGA) → Implementierungen mit SYCL (Intel oneAPI)

- FPGA-Entwicklungsplattform: BittWare IA-840f mit Intel Agilex 7 FPGA

**DREAM-Index**

Abfrage-Sequenzen

Knut Reinert, Enrico Seiler (FUB) Tobias Baumann, Mahnoor Maghroori, Thomas Steinke (ZIB) Christian Färber (Intel / Altera)

ntel altera

Gefördert durch: