Monolithically integrated load-break switch in JFET-based SiC technology

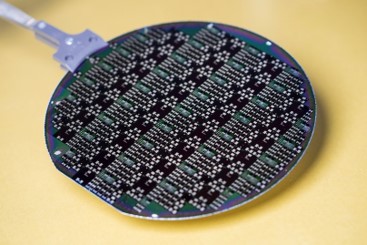

Complete 6'' SiC wafer with fabricated monolithic integrated load break switch devices.

"SiC-DCBreaker" chip after the separation process.

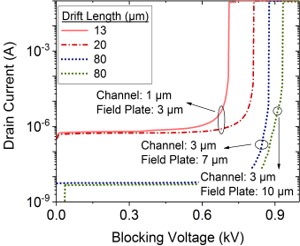

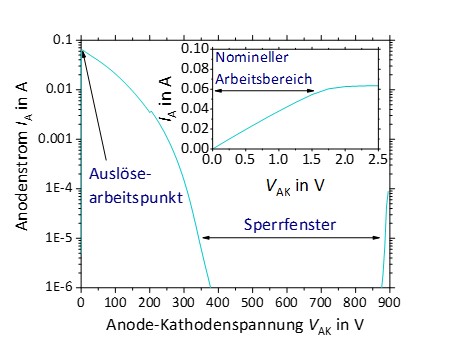

Measured output characteristic of a variant of the manufactured load-break switch components. The switch-disconnector carries the complete load current at all times. After the tripping current has been exceeded, the component immediately switches to blocking mode by itself. No external circuitry is required. The only requirement is that the DC link voltage is within the blocking window.

- First monolithically integrated realization of the "dual thyristor" in 4H-SiC JFET technology with potential for high-volume manufacturing.

- Self-powered, self-triggering and self-holding semiconductor-based fuse for DC grids and e-mobility applications

- The engineered topology enables scalability of trip current and reverse voltage for application-specific requirements

Cooperations:

- BMBF supported project „SiC-DCBreaker“03INT501BC

- In-house research at the Fraunhofer IISB

Publications:

- Boettcher N, Erlbacher T (2021): A Monolithically Integrated Circuit Breaker, in IEEE Electron Device Letters ( Volume: 42, Issue: 10, Oct. 2021). doi: 0.1109/LED.2021.3102935.

- Boettcher N, Erlbacher T (2020): Design Considerations on a Monolithically Integrated, Self Controlled and Regenerative 900 V SiC Circuit Breaker, in 2020 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia). doi: 10.1109/WiPDAAsia49671.2020.9360279.

- Huerner A, et al. (2017): Monolithically Integrated Solid-State-Circuit-Breaker for High Power Applications, in ICSCRM, Materials Science Forum Vol. 897, 2017. doi: 10.4028/www.scientific.net/msf.897.661

Further information:

Fraunhofer Group for Microelectronics in cooperation with the Leibniz institutes IHP and FBH

Fraunhofer Group for Microelectronics in cooperation with the Leibniz institutes IHP and FBH